全国2010年7月高等教育自学考试计算机组成原理试

X

温馨提示

亲爱的学员,您好!

全国2010年7月高等教育自学考试计算机组成原理试题

课程代码:02318

在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内.错选、多选或未选均无分.

1.若十进制数为115,则其对应的二进制数为( )

A.1100111

B.1011101

C.111001l

D.1111001

2.若十进制数为-65,则其对应的8位二进制补码(X)补为( )

A.10111110

B.01000001

C.11000001

D.1011111l

3.若16进制数为13F,则其对应的八进制数为( )

A.377

B.477

C.577

D.677

4.在下列存储器中,属于顺序存取存储器的是( )

A.U盘

B.光盘

C.磁盘

D.磁带

5.在下列浮点数的表示中,属于规格化编码的是( )

A.1.1011×2-3

B.1.001l×23

C.0.0101×2-3

D.0.001l×23

6.在一个计算机系统中,下列说法正确的是( )

A.主存的容量远大于Cache的容量,主存的速度比Cache快

B.主存的容量远小于Cache的容量,主存的速度比Cache快

C.主存的容量远大于Cache的容量,主存的速度比Cache慢

D.主存的容量远小于Cache的容量,主存的速度比Cache慢

7.在下列磁盘数据记录方式中,不具有自同步能力的方式是( )

A.FM

B.PM

C.NRZl

D.MFM

8.寄存器堆栈初始化时堆栈指针SP的值为( )

A.0

B.1

C.栈顶地址

D.最大地址

9.采用直接寻址方式的操作数存放在( )

A.某个寄存器中

B.某个存储器单元中

C.指令中

D.输入/输出端口中

10.微程序存放在( )

A.堆栈中

B.主存中

C.控制存储器中

D.磁盘中

11.比较硬连线控制器和微程序控制器,下列说法正确的是( )

A.硬连线控制器结构简单规整

B.硬连线控制器执行速度慢

C.微程序控制器执行速度快

D.微程序控制器容易实现复杂指令控制

12.下列说法正确的是( )

A.异步通信中不需要定时

B.同步通信的双方有各自独立的时钟信号

C.异步通信适宜于较快数据传送

D.同步通信适宜于较快数据传送

13.下列总线或接口中不属于串行方式的是( )

A.PCI

B.RS232

C.UART

D.USB

14.CPU响应中断请求是在( )

A.一个时钟周期结束时

B.一个总线周期结束时

C.一条指令结束时

D.一段程序结束时

15.控制DMA数据传送的是( )

A.DMA控制器

B.CPU

C.外设

D.主存

二、名词解释题(本大题共3小题,每小题3分,共9分)

16.中断嵌套

17.微地址寄存器

18.寻址方式

三、简答题(本大题共6小题,每小题5分,共30分)

19.简述CPU通过高速缓存Cache对主存的数据存取过程.

20.指令ADD R2,(2000)中包含了哪几种寻址方式?简述该指令的操作数的形成过程与功能.其中,源寻址为(2000),目的寻址为R2.

21.简述微程序控制的基本思想.

22.简述多重中断系统中CPU响应中断的步骤.

23.简述同步总线的定时方式.

24.试画出二进制数据序列10110的NRZ1、PM和FM的波形图.

四、简单应用题(本大题共2小题,每小题9分,共18分)

25.用Booth算法计算3×(-5)的4位补码乘法运算,要求写出其运算过程.

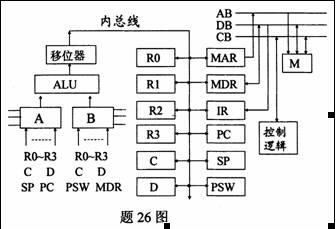

26.设有计算机的CPU数据通路及其与存储器的连接结构如下图所示,其中,R0~R3为通用寄存器,IR为指令寄存器,PC为程序计数器,SP为堆栈指针,C和D为暂存器,MAR为存储器地址寄存器,MDR为存储器数据缓冲寄存器.

试写出指令ADD R3,(R1)的执行流程.指令功能为加法操作,其中R3为采用寄存器寻址目的操作数,(R1)为采用寄存器间接寻址的源操作数.

五、设计题(本大题共1小题,13分)

27.用8K×8位/片的存储芯片构成32KB存储器,地址线为A15(高)~A0(低).

(1)需要几片这种存储芯片?

(2)32KB存储器共需要几位地址?是哪几位地址线?

(3)加至各芯片的地址线有几位?是哪几位地址线?

(4)用于产生片选信号的地址线是哪几位(译码法)?

《广东自考网》免责声明:

1、由于考试政策等各方面情况的调整与变化,本网提供的考试信息仅供参考,最终考试信息请以省考试院及院校官方发布的信息为准。

2、本站内容部分信息均来源网络收集整理或来源出处标注为其它媒体的稿件转载,免费转载出于非商业性学习目的,版权归原作者所有,如有内容与版权问题等请与本站联系。联系邮箱:812379481@qq.com