全国2008年4月高等教育自学考试计算机系统结构试

温馨提示

亲爱的学员,您好!

全国2008年4月高等教育自学考试

计算机系统结构试题

课程代码:02325

一、单项选择题(本大题共10小题,每小题1分,共10分)

在下列每小题的四个备选答案中选出一个正确答案,并将其字母标号填入题干的括号内.错选、多选或未选均无分.

1.系统程序员不透明的应当是( )

A.Cache存储器

B.虚拟存储器

C.指令缓冲寄存器

D.系列机各档不同的数据通路宽度

2."从中间开始"设计的"中间"目前多数在( )

A.传统机器语言机器级与操作系统机器级之间

B.传统机器语言机器级与微程序机器级之间

C.微程序机器级与汇编语言机器级之间

D.操作系统机器级与汇编语言机器级之间

3.计算机中优化使用的操作码编码方法是( )

A.哈夫曼编码

B.ASCII码

C.BCD码

D.扩展操作码

4.指令执行结果出现异常引起的中断是( )

A.输入/输出中断

B.机器校验中断

C.程序性中断

D.外部中断

5.以下不属于堆栈型替换算法的是( )

A.近期最少使用算法

B.近期最久未用过算法

C.先进先出算法

D.页面失效频率算法

6.以下与虚拟存储器的等效访问速度无关的是( )

A.页地址流

B.页面调度策略

C.主存的容量

D.辅存的容量

7.以下说法不正确的是( )

A.线性流水线是单功能流水线

B.动态流水线是多功能流水线

C.静态流水线是多功能流水线

D.动态流水线只能是单功能流水线

8.流水处理机对全局性相关的处理不包括( )

A.猜测法

B.提前形成条件码

C.加快短循环程序的执行

D.设置相关专用通路

9.拓扑结构用多级立方体网络,二功能交换单元,级控制方式,这种网络称为( )

A.Omega网络

B.交换网络

C.间接二进制n方体网络

D.数据变换网络

10.能实现作业、任务级并行的异构型多处理机属( )

A.SIMD

B.MISD

C.MIMD

D.SISD

二、填空题(本大题共10小题,每小题2分,共20分)

请在每小题的空格中填上正确答案.错填、不填均无分.

11.多机系统的耦合度可以分为最低耦合、___________耦合和___________耦合.

12.开发计算机系统结构并行性的主要技术途径有时间重叠、___________和___________.

13.自定义数据表示包括___________数据表示和___________两类.

14.系统效率是否提高是引入数据表示的一条重要原则,它表现在是否减少了实现的___________和所需的___________.

15.在满足通道设计流量不低于设备工作时的最大流量时,为使微观上不丢失设备信息,可

以加设___________或动态提高响应的___________来弥补.

16.Cache存储器若采用全相联映象规则,则主存中___________块都可映象装入到Cache中___________块的位置上.

17.流水线消除速度瓶颈的方法有瓶颈子过程___________和瓶颈子过程___________两种.

18.流水有部件级、处理机级、系统级等不同等级,多个处理机之间的流水属于___________

级流水,也称___________流水.

19.不同的多级互连网络,在所用的___________、拓扑结构和___________上各有不同.

20.多处理机的互连形式一般有总线形式、环形互连形式、___________形式、多端口存储器形式和___________形式等几种.

三、简答题(本大题共5小题,每小题6分,共30分)

21.简述多处理机要解决的主要技术问题(至少写出6个).

22.总线控制方式有哪三种?各需要增加几根用于总线控制的控制线?并说明每种方式优先级的灵活性.

23.实现软件移植的途径有哪些?各受什么限制?

24.什么是全排列网络?实现全排列网络有哪两种方法?

25.解决计算机主存与CPU的速度差对机器性能的影响,可采用哪三种解决方法?

四、简单应用题(本大题共2小题,每小题10分,共20分)

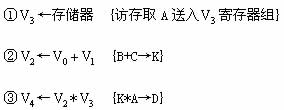

26.求向量D=A*(B+C),各向量元素个数均为6,参照CRAY-1方式分解为3条向量指令:

当采用下列2种方式工作时各需多少拍才能得到全部结果?

(1)①和②并行执行完后,再执行③;

(2)采用链接技术.

(注:CRAY-1方式启动访存1拍,访存6拍,打入寄存器组1拍,加法6拍,乘7拍)

27.Cache-主存存储层次中,主存有0~7共8块,Cache为4块,采用组相联映象.假设Cache已先后访问并预取进了主存的第5、1、3、7块,现访存地址流又为1、2、4、1、3、7、0、1、2、5、4、6时:

(1)画出用LRU替换算法,Cache内各块的实际替换过程图,并标出命中时刻,其中Cache分为两组.

(2)求出在此期间的Cache命中率.

五、综合应用题(本大题共2小题,每小题10分,共20分)

28.(1)要将浮点数尾数下溢处理成K—1位结果,则ROM表的单元数和字长各是多少?并简述ROM表各单元所填的内容与其地址之间的规则.

(2)若3位数,其最低位为下溢处理前的附加位,现将其下溢处理成2位结果,设计使下溢处理平均误差接近于零的ROM表,以表明地址单元与其内容的关系.

29.并行处理机有16个处理单元,若用STARAN网互连,

(1)画出4级立方体互连网络拓扑结构图;

(2)要实现2传给F,标出各级交换开关的状态.

《广东自考网》免责声明:

1、由于考试政策等各方面情况的调整与变化,本网提供的考试信息仅供参考,最终考试信息请以省考试院及院校官方发布的信息为准。

2、本站内容部分信息均来源网络收集整理或来源出处标注为其它媒体的稿件转载,免费转载出于非商业性学习目的,版权归原作者所有,如有内容与版权问题等请与本站联系。联系邮箱:812379481@qq.com